清華新聞網(wǎng)9月15日電 當(dāng)前,生成式人工智能已引爆新一輪智能革命的發(fā)展浪潮,大算力支撐下的人工智能技術(shù)極大改變著人類的生產(chǎn)生活方式。可隨之而來的海量參數(shù)令算力需求持續(xù)攀升,如何解決龐大的算力缺口,實(shí)現(xiàn)能效比的大幅提升,正在變得日益迫切。高算力、高能效芯片作為算力的具體載體,已成為驅(qū)動(dòng)本輪智能革命發(fā)展的核心底座,更是推動(dòng)人類社會(huì)不斷發(fā)展的動(dòng)力源泉。

面向傳統(tǒng)存算分離架構(gòu)制約算力提升的重大挑戰(zhàn),清華大學(xué)集成電路學(xué)院吳華強(qiáng)教授、高濱副教授聚焦憶阻器存算一體技術(shù)研究,探索實(shí)現(xiàn)計(jì)算機(jī)系統(tǒng)新范式。憶阻器存算一體技術(shù)從底層器件、電路架構(gòu)和計(jì)算理論全面顛覆了馮·諾依曼傳統(tǒng)計(jì)算架構(gòu),可實(shí)現(xiàn)算力和能效的跨越式提升,同時(shí),該技術(shù)還可利用底層器件的學(xué)習(xí)特性,支持實(shí)時(shí)片上學(xué)習(xí),賦能基于本地學(xué)習(xí)的邊緣訓(xùn)練新場(chǎng)景。當(dāng)前國際上的相關(guān)研究主要集中在憶阻器陣列層面的學(xué)習(xí)功能演示,然而實(shí)現(xiàn)全系統(tǒng)集成的、支持高效片上學(xué)習(xí)的憶阻器芯片仍面臨較大挑戰(zhàn),至今還未實(shí)現(xiàn),主要在于傳統(tǒng)的反向傳播訓(xùn)練算法所要求的高精度權(quán)重更新方式與憶阻器實(shí)際特性的適配性較差。

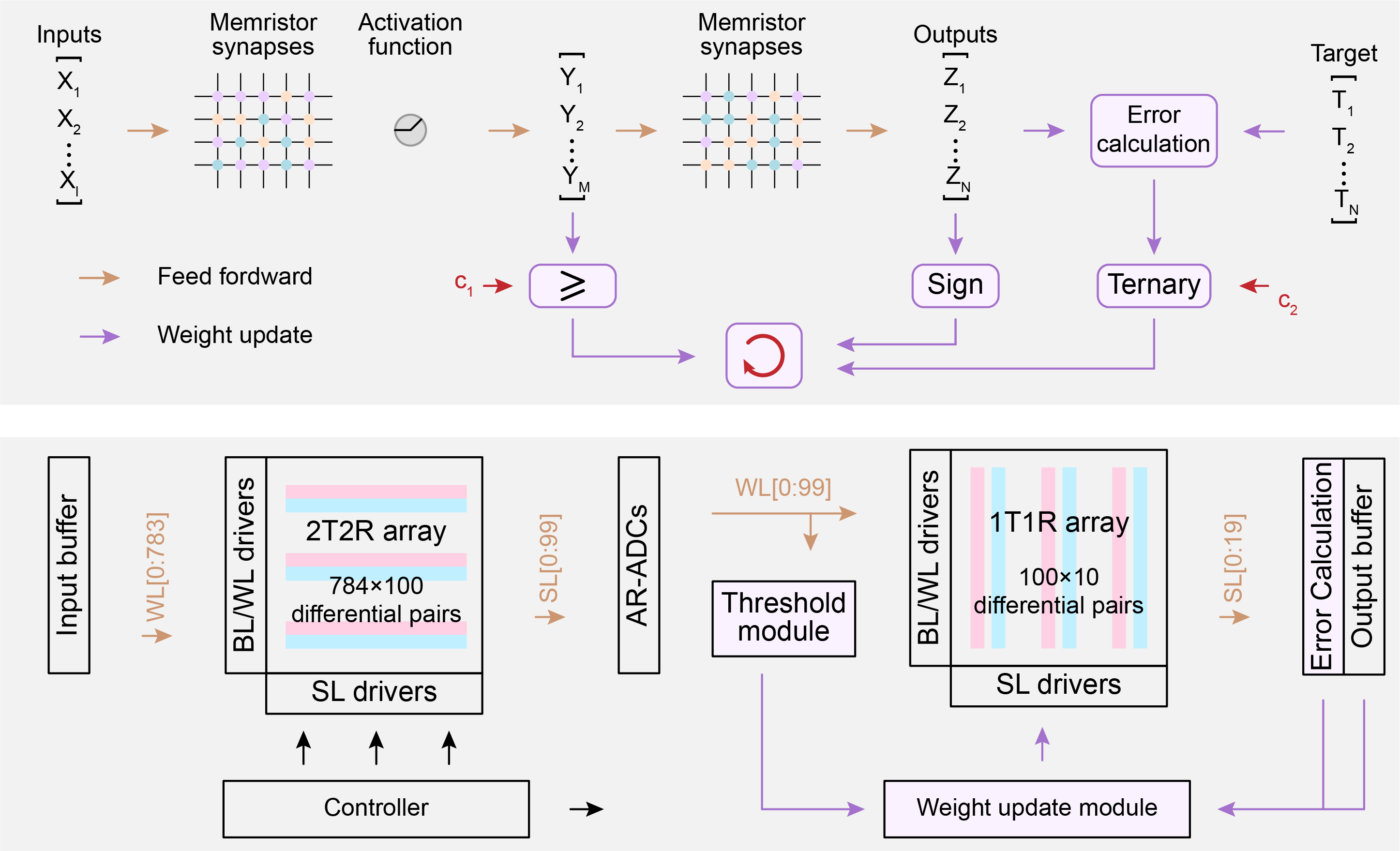

為解決上述難題,課題組基于存算一體計(jì)算范式,創(chuàng)造性提出適配憶阻器存算一體實(shí)現(xiàn)高效片上學(xué)習(xí)的新型通用算法和架構(gòu)(STELLAR),有效實(shí)現(xiàn)大規(guī)模模擬型憶阻器陣列與CMOS的單片三維集成,通過算法、架構(gòu)、集成方式的全流程協(xié)同創(chuàng)新,研制出全球首顆全系統(tǒng)集成的、支持高效片上學(xué)習(xí)的憶阻器存算一體芯片。該芯片包含支持完整片上學(xué)習(xí)所必需的全部電路模塊,成功完成圖像分類、語音識(shí)別和控制任務(wù)等多種片上增量學(xué)習(xí)功能驗(yàn)證,展示出高適應(yīng)性、高能效、高通用性、高準(zhǔn)確率等特點(diǎn),有效強(qiáng)化了智能設(shè)備在實(shí)際應(yīng)用場(chǎng)景下的學(xué)習(xí)適應(yīng)能力。相同任務(wù)下,該芯片實(shí)現(xiàn)片上學(xué)習(xí)的能耗僅為先進(jìn)工藝下專用集成電路(ASIC)系統(tǒng)的3%,展現(xiàn)出卓越的能效優(yōu)勢(shì),極具滿足人工智能時(shí)代高算力需求的應(yīng)用潛力,為突破馮·諾依曼傳統(tǒng)計(jì)算架構(gòu)下的能效瓶頸提供了一種創(chuàng)新發(fā)展路徑。

憶阻器存算一體芯片及測(cè)試系統(tǒng)

基于憶阻器存算一體實(shí)現(xiàn)高效片上學(xué)習(xí)的通用算法和架構(gòu)

近日,該研究成果以“面向邊緣學(xué)習(xí)的全集成類腦憶阻器芯片”(Edge Learning Using a Fully Integrated Neuro-Inspired Memristor Chip)為題在線發(fā)表在《科學(xué)》(Science)上。

論文通訊作者為清華大學(xué)集成電路學(xué)院高濱副教授和吳華強(qiáng)教授,清華大學(xué)集成電路學(xué)院博士生張文彬、博士后姚鵬為論文的共同第一作者,其他參加研究的作者包括清華大學(xué)集成電路學(xué)院錢鶴教授、唐建石副教授、伍冬副研究員、張清天助理研究員,清華大學(xué)電子系汪玉教授等。

該研究得到科技部科技創(chuàng)新2030“腦科學(xué)與類腦研究”重大項(xiàng)目、國家自然科學(xué)基金委后摩爾重大研究計(jì)劃、北京集成電路高精尖中心等的支持。

論文鏈接:

https://www.science.org/doi/full/10.1126/science.ade3483

供稿:集成電路學(xué)院

題圖設(shè)計(jì):李娜

編輯:李華山

審核:郭玲