清華新聞網(wǎng)1月30日電 1月22日至25日,由國(guó)際電氣電子工程師學(xué)會(huì)(IEEE)主辦的2024年亞洲及南太平洋設(shè)計(jì)自動(dòng)化會(huì)議(IEEE ASP-DAC 2024)在韓國(guó)仁川舉行,全球設(shè)計(jì)自動(dòng)化領(lǐng)域的400余位研究者參會(huì)。清華大學(xué)電子工程系教授楊華中、汪玉于2014年發(fā)表在ASP-DAC會(huì)議的論文“自訓(xùn)練:面向基于憶阻器神經(jīng)網(wǎng)絡(luò)加速器的混合信號(hào)訓(xùn)練加速”(Train Itself:Mixed-Signal Training Acceleration for Memristor-based Neural Network)榮獲該會(huì)議十年回顧最具影響力論文獎(jiǎng)。

獲獎(jiǎng)?wù)掌?/p>

獲獎(jiǎng)證書

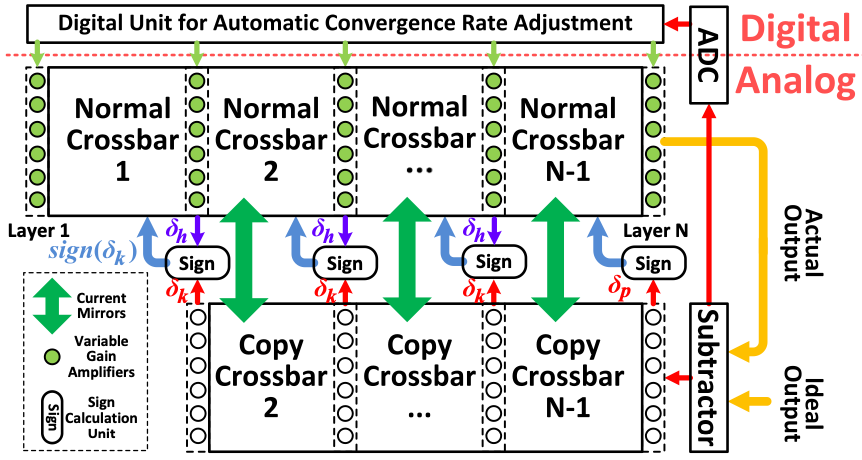

基于憶阻器的存算一體架構(gòu)(Process-In-Memory, PIM)可以在存儲(chǔ)陣列內(nèi)完成計(jì)算,顯著降低數(shù)據(jù)搬運(yùn)的能量開(kāi)銷,高效實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)算法。現(xiàn)有存算一體架構(gòu)往往需要使用GPU對(duì)神經(jīng)網(wǎng)絡(luò)模型進(jìn)行訓(xùn)練,再將訓(xùn)練后的模型部署在憶阻器器件中,訓(xùn)練成本高昂。針對(duì)這一問(wèn)題,本文提出了一種直接在憶阻器陣列中實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)訓(xùn)練的系統(tǒng)方案。通過(guò)設(shè)計(jì)一系列數(shù)模混合輔助運(yùn)算結(jié)構(gòu)和算法近似化方法,首次實(shí)現(xiàn)了基于憶阻器計(jì)算架構(gòu)的神經(jīng)網(wǎng)絡(luò)自訓(xùn)練,有望將神經(jīng)網(wǎng)絡(luò)訓(xùn)練能效提高3至4個(gè)量級(jí)。

技術(shù)方案

電子工程系校友、2013級(jí)碩士李伯勛為該論文第一作者,汪玉為該論文通訊作者,論文其他合作作者包括電子工程系校友、2012級(jí)博士汪彧之,美國(guó)杜克大學(xué)教授、電子工程系校友陳怡然以及楊華中。

ASP-DAC是超大規(guī)模集成電路設(shè)計(jì)、電子設(shè)計(jì)自動(dòng)化(EDA)和芯片制備領(lǐng)域的高水平國(guó)際學(xué)術(shù)會(huì)議,始于1995年。ASP-DAC十年回顧最具影響力論文獎(jiǎng)旨在表彰在過(guò)去十年中對(duì)EDA領(lǐng)域產(chǎn)生重大影響的ASP-DAC論文,獲得此獎(jiǎng)項(xiàng)的論文對(duì)學(xué)術(shù)界與工業(yè)界產(chǎn)生了持久影響,并被廣泛引用。

供稿:電子系

編輯:李華山

審核:郭玲