清華新聞網(wǎng)3月18日電 儲備池計算(Reservoir computing)是一種適用于高效處理時序信號的仿生神經(jīng)網(wǎng)絡(luò),物理儲備池計算能夠高效地挖掘電子器件的動態(tài)特性作為計算資源,用于硬件實現(xiàn)循環(huán)神經(jīng)網(wǎng)絡(luò),通過復(fù)雜的遞歸動力學(xué)機(jī)制對輸入信號進(jìn)行非線性映射和信息編碼,具有高效簡潔、易于實現(xiàn)全模擬和全并行計算等優(yōu)勢,逐漸成為類腦計算領(lǐng)域的一個熱點研究方向,在人工智能、邊緣計算、非線性系統(tǒng)等領(lǐng)域具有廣泛的應(yīng)用前景。

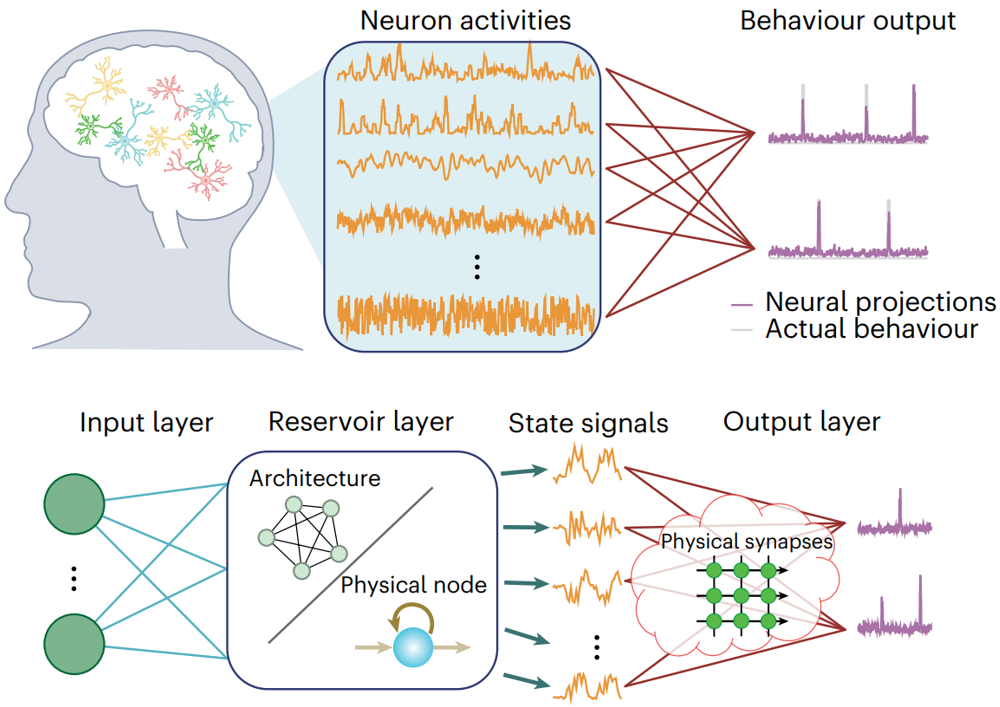

圖1.作為一種新型類腦計算架構(gòu),物理儲備池計算系統(tǒng)包含輸入、輸出和儲備池層,可高效處理時序信號

近日,清華大學(xué)集成電路學(xué)院唐建石副教授、吳華強(qiáng)教授與合作者在《自然·電子》(Nature Electronics)發(fā)表了題為“基于新型電子器件的物理儲備池計算”(Physical reservoir computing with emerging electronics)的綜述文章,系統(tǒng)梳理了基于新型電子器件的物理儲備池計算的起源、發(fā)展與未來展望,重點分析了儲備池架構(gòu)、物理節(jié)點、輸出層等構(gòu)筑一個完整物理儲備池系統(tǒng)的關(guān)鍵技術(shù)。

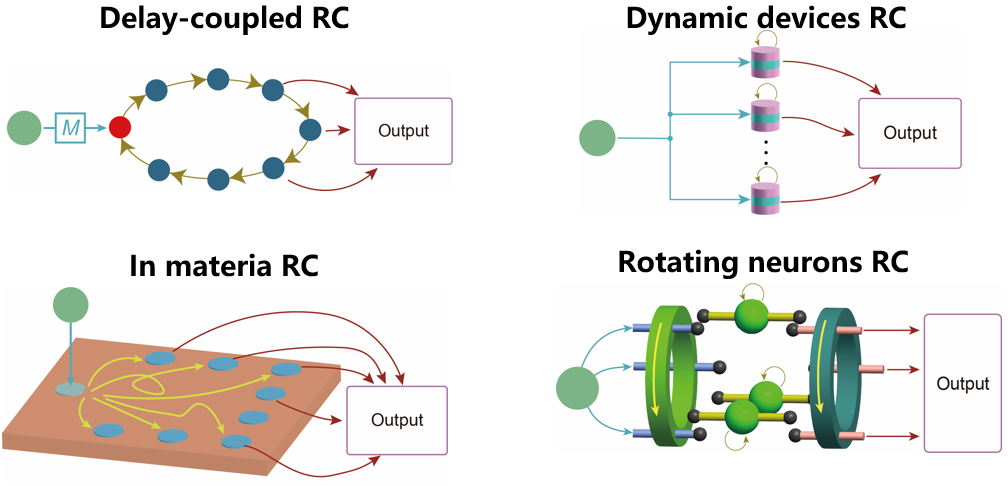

文章首先將物理儲備池計算的實現(xiàn)架構(gòu)分為四大類,包括時延耦合儲備池(Delay-coupled RC)、動態(tài)器件儲備池(Dynamic devices RC)、材料內(nèi)計算儲備池(In materia RC)、旋轉(zhuǎn)神經(jīng)元儲備池(Rotating neurons RC),這些架構(gòu)定義了儲備池層中物理節(jié)點的拓?fù)溥B接關(guān)系。國內(nèi)外研究團(tuán)隊嘗試各種不同物理節(jié)點在這些架構(gòu)下實現(xiàn)儲備池,包括憶阻器、自旋電子器件、鐵電場效應(yīng)晶體管、納米線網(wǎng)絡(luò)等,用于模擬神經(jīng)元的非線性和動態(tài)特性。除物理節(jié)點外,文章還介紹了物理儲備池計算中預(yù)處理技術(shù)和輸出層的設(shè)計方法,探討了相應(yīng)的優(yōu)化策略與基準(zhǔn)任務(wù)。在此基礎(chǔ)上,文章詳細(xì)對比了文獻(xiàn)中各種實現(xiàn)物理儲備池計算的硬件開銷和綜合性能,提出了系統(tǒng)設(shè)計的工具箱。

圖2.四種典型的物理儲備池計算架構(gòu)

從硬件實現(xiàn)方式的角度看,儲備池計算的發(fā)展大致經(jīng)歷三個階段,自2001年提出儲備池計算的原型—回聲狀態(tài)網(wǎng)絡(luò)(ESN)后,最初十年的研究聚焦于算法方面,采用全數(shù)字的實現(xiàn)方式;第二個十年的研究進(jìn)一步嘗試了不同的架構(gòu)和物理節(jié)點在模擬域?qū)崿F(xiàn)儲備池層,但輸出層仍采用數(shù)字方式實現(xiàn),代表數(shù)模混合的實現(xiàn)階段;近幾年的研究則開始更多關(guān)注一個全模擬的完整物理儲備池計算系統(tǒng),包括采用模擬型憶阻器陣列作為輸出層,以降低整體功耗和硬件開銷。當(dāng)前,物理儲備池計算正處于蓬勃發(fā)展階段,國內(nèi)外研究已充分論證物理儲備池計算的原理和可行性,未來在架構(gòu)、算法、物理節(jié)點、硬件實現(xiàn)、應(yīng)用等方面具有廣闊的發(fā)展機(jī)遇,其性能邊界與應(yīng)用領(lǐng)域?qū)玫竭M(jìn)一步拓展。

圖3.儲備池計算的發(fā)展脈絡(luò)與未來機(jī)遇

近年來,清華大學(xué)集成電路學(xué)院研究團(tuán)隊圍繞儲備池計算開展了深入研究,構(gòu)筑了基于動態(tài)憶阻器的并行儲備池計算系統(tǒng),提出了旋轉(zhuǎn)神經(jīng)元儲備池架構(gòu),研制了基于動態(tài)和非易失型憶阻器的完整儲備池系統(tǒng),并首次實現(xiàn)了端到端的全模擬信號處理。

清華大學(xué)集成電路學(xué)院唐建石副教授為論文通訊作者,清華大學(xué)“水木學(xué)者”博士后梁向鵬為論文第一作者,共同作者包括清華大學(xué)集成電路學(xué)院吳華強(qiáng)教授、錢鶴教授、高濱副教授及蘇州大學(xué)功能納米與軟物質(zhì)研究院仲亞楠副教授,清華大學(xué)集成電路學(xué)院為本論文的第一單位。研究得到國家自然科學(xué)基金委、科技部科技創(chuàng)新2030-重大項目、北京信息科學(xué)與技術(shù)國家研究中心、科學(xué)探索獎、高精尖創(chuàng)新中心“未來芯片學(xué)者支持計劃”等的支持。

論文鏈接:

https://www.nature.com/articles/s41928-024-01133-z

供稿:集成電路學(xué)院

編輯:李華山

審核:郭玲